|

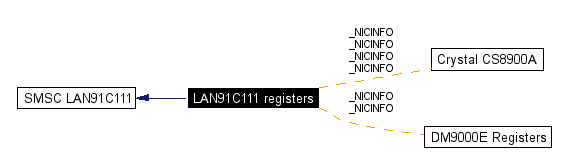

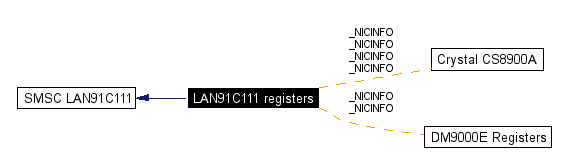

Collaboration diagram for LAN91C111 registers:

|

Data Structures | |

| struct | _NICINFO |

| Network interface controller information structure. More... | |

| struct | _NICINFO |

| Network interface controller information structure. More... | |

Defines | |

| #define | NIC_BSR (LANC111_BASE_ADDR + 0x0E) |

| Bank select register. | |

| #define | NIC_TCR (LANC111_BASE_ADDR + 0x00) |

| Bank 0 - Transmit control register. | |

| #define | TCR_SWFDUP 0x8000 |

| #define | TCR_EPH_LOOP 0x2000 |

| #define | TCR_STP_SQET 0x1000 |

| #define | TCR_FDUPLX 0x0800 |

| #define | TCR_MON_CSN 0x0400 |

| #define | TCR_NOCRC 0x0100 |

| #define | TCR_PAD_EN 0x0080 |

| #define | TCR_FORCOL 0x0004 |

| #define | TCR_LOOP 0x0002 |

| #define | TCR_TXENA 0x0001 |

| #define | NIC_EPHSR (LANC111_BASE_ADDR + 0x02) |

| Bank 0 - EPH status register. | |

| #define | NIC_RCR (LANC111_BASE_ADDR + 0x04) |

| Bank 0 - Receive control register. | |

| #define | RCR_SOFT_RST 0x8000 |

| #define | RCR_FILT_CAR 0x4000 |

| #define | RCR_ABORT_ENB 0x2000 |

| #define | RCR_STRIP_CRC 0x0200 |

| #define | RCR_RXEN 0x0100 |

| #define | RCR_ALMUL 0x0004 |

| #define | RCR_PRMS 0x0002 |

| #define | RCR_RX_ABORT 0x0001 |

| #define | NIC_ECR (LANC111_BASE_ADDR + 0x06) |

| Bank 0 - Counter register. | |

| #define | NIC_MIR (LANC111_BASE_ADDR + 0x08) |

| Bank 0 - Memory information register. | |

| #define | NIC_RPCR (LANC111_BASE_ADDR + 0x0A) |

| Bank 0 - Receive / PHY control register. | |

| #define | RPCR_SPEED 0x2000 |

| #define | RPCR_DPLX 0x1000 |

| #define | RPCR_ANEG 0x0800 |

| #define | RPCR_LEDA_PAT 0x0000 |

| #define | RPCR_LEDB_PAT 0x0010 |

| #define | NIC_CR (LANC111_BASE_ADDR + 0x00) |

| Bank 1 - Configuration register. | |

| #define | CR_EPH_EN 0x8000 |

| #define | NIC_BAR (LANC111_BASE_ADDR + 0x02) |

| Bank 1 - Base address register. | |

| #define | NIC_IAR (LANC111_BASE_ADDR + 0x04) |

| Bank 1 - Individual address register. | |

| #define | NIC_GPR (LANC111_BASE_ADDR + 0x0A) |

| Bank 1 - General purpose register. | |

| #define | NIC_CTR (LANC111_BASE_ADDR + 0x0C) |

| Bank 1 - Control register. | |

| #define | CTR_RCV_BAD 0x4000 |

| #define | CTR_AUTO_RELEASE 0x0800 |

| #define | NIC_MMUCR (LANC111_BASE_ADDR + 0x00) |

| Bank 2 - MMU command register. | |

| #define | MMUCR_BUSY 0x0001 |

| #define | MMU_NOP 0 |

| #define | MMU_ALO (1<<5) |

| #define | MMU_RST (2<<5) |

| #define | MMU_REM (3<<5) |

| #define | MMU_TOP (4<<5) |

| #define | MMU_PKT (5<<5) |

| #define | MMU_ENQ (6<<5) |

| #define | MMU_RTX (7<<5) |

| #define | NIC_PNR (LANC111_BASE_ADDR + 0x02) |

| Bank 2 - Packet number register. | |

| #define | NIC_ARR (LANC111_BASE_ADDR + 0x03) |

| Bank 2 - Allocation result register. | |

| #define | ARR_FAILED 0x80 |

| #define | NIC_FIFO (LANC111_BASE_ADDR + 0x04) |

| Bank 2 - FIFO ports register. | |

| #define | NIC_PTR (LANC111_BASE_ADDR + 0x06) |

| Bank 2 - Pointer register. | |

| #define | PTR_RCV 0x8000 |

| #define | PTR_AUTO_INCR 0x4000 |

| #define | PTR_READ 0x2000 |

| #define | PTR_ETEN 0x1000 |

| #define | PTR_NOT_EMPTY 0x0800 |

| #define | NIC_DATA (LANC111_BASE_ADDR + 0x08) |

| Bank 2 - Data register. | |

| #define | NIC_IST (LANC111_BASE_ADDR + 0x0C) |

| Bank 2 - Interrupt status register. | |

| #define | NIC_ACK (LANC111_BASE_ADDR + 0x0C) |

| Bank 2 - Interrupt acknowledge register. | |

| #define | NIC_MSK (LANC111_BASE_ADDR + 0x0D) |

| Bank 2 - Interrupt mask register. | |

| #define | INT_MD 0x80 |

| PHY state change interrupt bit mask. | |

| #define | INT_ERCV 0x40 |

| Early receive interrupt bit mask. | |

| #define | INT_EPH 0x20 |

| Ethernet protocol interrupt bit mask. | |

| #define | INT_RX_OVRN 0x10 |

| Receive overrun interrupt bit mask. | |

| #define | INT_ALLOC 0x08 |

| Transmit allocation interrupt bit mask. | |

| #define | INT_TX_EMPTY 0x04 |

| Transmitter empty interrupt bit mask. | |

| #define | INT_TX 0x02 |

| Transmit complete interrupt bit mask. | |

| #define | INT_RCV 0x01 |

| Receive interrupt bit mask. | |

| #define | NIC_MT (LANC111_BASE_ADDR + 0x00) |

| Bank 3 - Multicast table register. | |

| #define | NIC_MGMT (LANC111_BASE_ADDR + 0x08) |

| Bank 3 - Management interface register. | |

| #define | MGMT_MDOE 0x08 |

| #define | MGMT_MCLK 0x04 |

| #define | MGMT_MDI 0x02 |

| #define | MGMT_MDO 0x01 |

| #define | NIC_REV (LANC111_BASE_ADDR + 0x0A) |

| Bank 3 - Revision register. | |

| #define | NIC_ERCV (LANC111_BASE_ADDR + 0x0C) |

| Bank 3 - Early RCV register. | |

| #define | NIC_PHYCR 0 |

| PHY control register. | |

| #define | PHYCR_RST 0x8000 |

| #define | PHYCR_LPBK 0x4000 |

| #define | PHYCR_SPEED 0x2000 |

| #define | PHYCR_ANEG_EN 0x1000 |

| #define | PHYCR_PDN 0x0800 |

| #define | PHYCR_MII_DIS 0x0400 |

| #define | PHYCR_ANEG_RST 0x0200 |

| #define | PHYCR_DPLX 0x0100 |

| #define | PHYCR_COLST 0x0080 |

| #define | NIC_PHYSR 1 |

| PHY status register. | |

| #define | PHYSR_CAP_T4 0x8000 |

| #define | PHYSR_CAP_TXF 0x4000 |

| #define | PHYSR_CAP_TXH 0x2000 |

| #define | PHYSR_CAP_TF 0x1000 |

| #define | PHYSR_CAP_TH 0x0800 |

| #define | PHYSR_CAP_SUPR 0x0040 |

| #define | PHYSR_ANEG_ACK 0x0020 |

| #define | PHYSR_REM_FLT 0x0010 |

| #define | PHYSR_CAP_ANEG 0x0008 |

| #define | PHYSR_LINK 0x0004 |

| #define | PHYSR_JAB 0x0002 |

| #define | PHYSR_EXREG 0x0001 |

| #define | NIC_PHYID1 2 |

| PHY identifier register 1. | |

| #define | NIC_PHYID2 3 |

| PHY identifier register 1. | |

| #define | NIC_PHYANAD 4 |

| PHY auto-negotiation advertisement register. | |

| #define | PHYANAD_NP 0x8000 |

| #define | PHYANAD_ACK 0x4000 |

| #define | PHYANAD_RF 0x2000 |

| #define | PHYANAD_T4 0x0200 |

| #define | PHYANAD_TX_FDX 0x0100 |

| #define | PHYANAD_TX_HDX 0x0080 |

| #define | PHYANAD_10FDX 0x0040 |

| #define | PHYANAD_10_HDX 0x0020 |

| #define | PHYANAD_CSMA 0x0001 |

| #define | NIC_PHYANRC 5 |

| PHY auto-negotiation remote end capability register. | |

| #define | NIC_PHYCFR1 16 |

| PHY configuration register 1. | |

| #define | NIC_PHYCFR2 17 |

| PHY configuration register 2. | |

| #define | NIC_PHYSOR 18 |

| PHY status output register. | |

| #define | PHYSOR_INT 0x8000 |

| #define | PHYSOR_LNKFAIL 0x4000 |

| #define | PHYSOR_LOSSSYNC 0x2000 |

| #define | PHYSOR_CWRD 0x1000 |

| #define | PHYSOR_SSD 0x0800 |

| #define | PHYSOR_ESD 0x0400 |

| #define | PHYSOR_RPOL 0x0200 |

| #define | PHYSOR_JAB 0x0100 |

| #define | PHYSOR_SPDDET 0x0080 |

| #define | PHYSOR_DPLXDET 0x0040 |

| #define | NIC_PHYMSK 19 |

| PHY mask register. | |

| #define | PHYMSK_MINT 0x8000 |

| #define | PHYMSK_MLNKFAIL 0x4000 |

| #define | PHYMSK_MLOSSSYN 0x2000 |

| #define | PHYMSK_MCWRD 0x1000 |

| #define | PHYMSK_MSSD 0x0800 |

| #define | PHYMSK_MESD 0x0400 |

| #define | PHYMSK_MRPOL 0x0200 |

| #define | PHYMSK_MJAB 0x0100 |

| #define | PHYMSK_MSPDDT 0x0080 |

| #define | PHYMSK_MDPLDT 0x0040 |

| #define | MSBV(bit) (1 << ((bit) - 8)) |

| #define | nic_outlb(addr, val) (*(volatile u_char *)(addr) = (val)) |

| #define | nic_outhb(addr, val) (*(volatile u_char *)((addr) + 1) = (val)) |

| #define | nic_outwx(addr, val) (*(volatile u_short *)(addr) = (val)) |

| #define | nic_outw(addr, val) |

| #define | nic_inlb(addr) (*(volatile u_char *)(addr)) |

| #define | nic_inhb(addr) (*(volatile u_char *)((addr) + 1)) |

| #define | nic_inw(addr) (*(volatile u_short *)(addr)) |

| #define | nic_bs(bank) nic_outlb(NIC_BSR, bank) |

Typedefs | |

| typedef _NICINFO | NICINFO |

| Network interface controller information type. | |

|

|

NIC_TCR bit mask, enables full duplex. |

|

|

NIC_TCR bit mask, enables internal loopback. |

|

|

NIC_TCR bit mask, enables transmission stop on SQET error. |

|

|

NIC_TCR bit mask, enables receiving own frames. |

|

|

NIC_TCR bit mask, enables carrier monitoring. |

|

|

NIC_TCR bit mask, disables CRC transmission. |

|

|

NIC_TCR bit mask, enables automatic padding. |

|

|

NIC_TCR bit mask, forces collision. |

|

|

NIC_TCR bit mask, enables PHY loopback. |

|

|

NIC_TCR bit mask, enables transmitter. |

|

|

NIC_RCR bit mask, activates software reset. |

|

|

NIC_RCR bit mask, enables carrier filter. |

|

|

NIC_RCR bit mask, enables receive abort on collision. |

|

|

NIC_RCR bit mask, strips CRC. |

|

|

NIC_RCR bit mask, enables receiver. |

|

|

NIC_RCR bit mask, multicast frames accepted when set. |

|

|

NIC_RCR bit mask, enables promiscuous mode. |

|

|

NIC_RCR bit mask, set when receive was aborted. |

|

|

NIC_RPCR bit mask, PHY operates at 100 Mbps. |

|

|

NIC_RPCR bit mask, PHY operates at full duplex mode. |

|

|

NIC_RPCR bit mask, sets PHY in auto-negotiation mode. |

|

|

NIC_RPCR bit mask for LEDA mode. |

|

|

NIC_RPCR bit mask for LEDB mode. |

|

|

NIC_CR bit mask, . |

|

|

NIC_CTR bit mask. |

|

|

NIC_CTR bit mask, transmit packets automatically released. |

|

|

Bank 2 - Packet number register. This byte register specifies the accessible transmit packet number. |

|

|

Bank 2 - Allocation result register. This byte register is updated upon a MMU_ALO command. |

|

|

NIC_MGMT bit mask, enables MDO pin. |

|

|

NIC_MGMT bit mask, drives MDCLK pin. |

|

|

NIC_MGMT bit mask, reflects MDI pin status. |

|

|

NIC_MGMT bit mask, drives MDO pin. |

|

|

NIC_PHYCR bit mask, resets PHY. |

|

|

NIC_PHYCR bit mask, . |

|

|

NIC_PHYCR bit mask, . |

|

|

NIC_PHYCR bit mask, . |

|

|

NIC_PHYCR bit mask, . |

|

|

NIC_PHYCR bit mask, . |

|

|

NIC_PHYCR bit mask, . |

|

|

NIC_PHYCR bit mask, . |

|

|

NIC_PHYCR bit mask, . |

|

|

NIC_PHYSR bit mask, indicates 100BASE-T4 capability. |

|

|

NIC_PHYSR bit mask, indicates 100BASE-TX full duplex capability. |

|

|

NIC_PHYSR bit mask, indicates 100BASE-TX half duplex capability. |

|

|

NIC_PHYSR bit mask, indicates 10BASE-T full duplex capability. |

|

|

NIC_PHYSR bit mask, indicates 10BASE-T half duplex capability. |

|

|

NIC_PHYSR bit mask, indicates preamble suppression capability. |

|

|

NIC_PHYSR bit mask, auto-negotiation completed. |

|

|

NIC_PHYSR bit mask, remote fault detected. |

|

|

NIC_PHYSR bit mask, indicates auto-negotiation capability. |

|

|

NIC_PHYSR bit mask, valid link status. |

|

|

NIC_PHYSR bit mask, jabber collision detected. |

|

|

NIC_PHYSR bit mask, extended capabilities available. |

|

|

NIC_PHYANAD bit mask, exchanging next page information. |

|

|

NIC_PHYANAD bit mask, acknowledged. |

|

|

NIC_PHYANAD bit mask, remote fault. |

|

|

NIC_PHYANAD bit mask, indicates 100BASE-T4 capability. |

|

|

NIC_PHYANAD bit mask, indicates 100BASE-TX full duplex capability. |

|

|

NIC_PHYANAD bit mask, indicates 100BASE-TX half duplex capability. |

|

|

NIC_PHYANAD bit mask, indicates 10BASE-T full duplex capability. |

|

|

NIC_PHYANAD bit mask, indicates 10BASE-T half duplex capability. |

|

|

NIC_PHYANAD bit mask, indicates 802.3 CSMA capability. |

|

|

NIC_PHYSOR bit mask, interrupt bits changed. |

|

|

NIC_PHYSOR bit mask, link failure detected. |

|

|

NIC_PHYSOR bit mask, descrambler sync lost detected. |

|

|

NIC_PHYSOR bit mask, code word error detected. |

|

|

NIC_PHYSOR bit mask, start of stream error detected. |

|

|

NIC_PHYSOR bit mask, end of stream error detected. |

|

|

NIC_PHYSOR bit mask, reverse polarity detected. |

|

|

NIC_PHYSOR bit mask, jabber detected. |

|

|

NIC_PHYSOR bit mask, 100/10 speed detected. |

|

|

NIC_PHYSOR bit mask, duplex detected. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_INT interrupt. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_LNKFAIL interrupt. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_LOSSSYNC interrupt. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_CWRD interrupt. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_SSD interrupt. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_ESD interrupt. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_RPOL interrupt. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_JAB interrupt. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_SPDDET interrupt. |

|

|

NIC_PHYMSK bit mask, enables PHYSOR_DPLXDET interrupt. |

|

|

Value: |